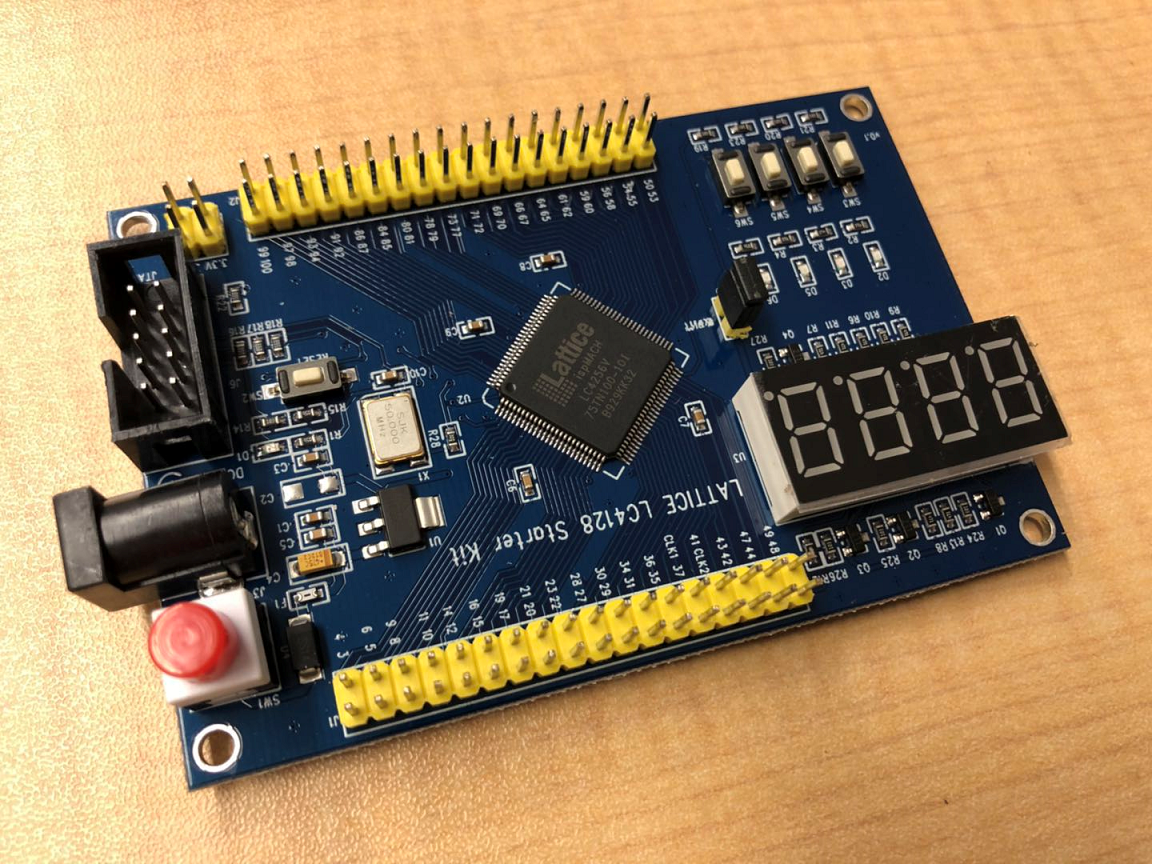

Lattice(ラティス)CPLD、ispMACH4000ファミリのLC4256V開発ボード

メインチップはLATTICE社の超高速低電力消費CPLD、ispMACH 4000シリーズのLC4256V75TN100を採用。

50MHz水晶発振器搭載、JTAGインタフェース搭載、CPUのすべてのピンを2.54mm拡張ヘッダで引出、キー、LED、7SEG LEDなど基本拡張回路付き

日本語マニュアル、サンプルソース提供。初心者でもはじめやすい!

製品仕様

-

メインチップ:

- LATTICE社の超高速低電力消費CPLD、ispMACH 4000シリーズのLC4256V75TN100を採用 クロック:

- 50MHz水晶発振器搭載 インタフェース:

- 10pin(5x2列)のJTAGインタフェース搭載

- CPUのすべてのピンを2.54mm拡張ヘッダで引き出される キーと表示:

- ユーザキー x 4

- リセットキー x 1、ユーザキーとして利用可

- ユーザLED x 4、電源指示LED x 1

- 4桁7SEG LED x 1 電源:

- 5V DC電源コネクタ、プラグサイズ:外径:5.5mm 内径:2.1mm

- Self-locking電源スイッチ搭載 その他:

- 外形寸法: 90×60(mm) ※突起物は除く

各種資料

| マニュアル: | LATTICE_CPLD_LC4256_manual.pdf |

| 回路図: | LC4256-sch.pdf |

| データシート: | Datasheet.zip |

| サンプルソース: | Example.zip |

★その他、アフターフォローは電話・メールで専門技術者がいつでも受け付けておりので、

製品使用に関するご心配は一切ございません。

商品カテゴリ

カレンダー

- ■今日

- ■定休日